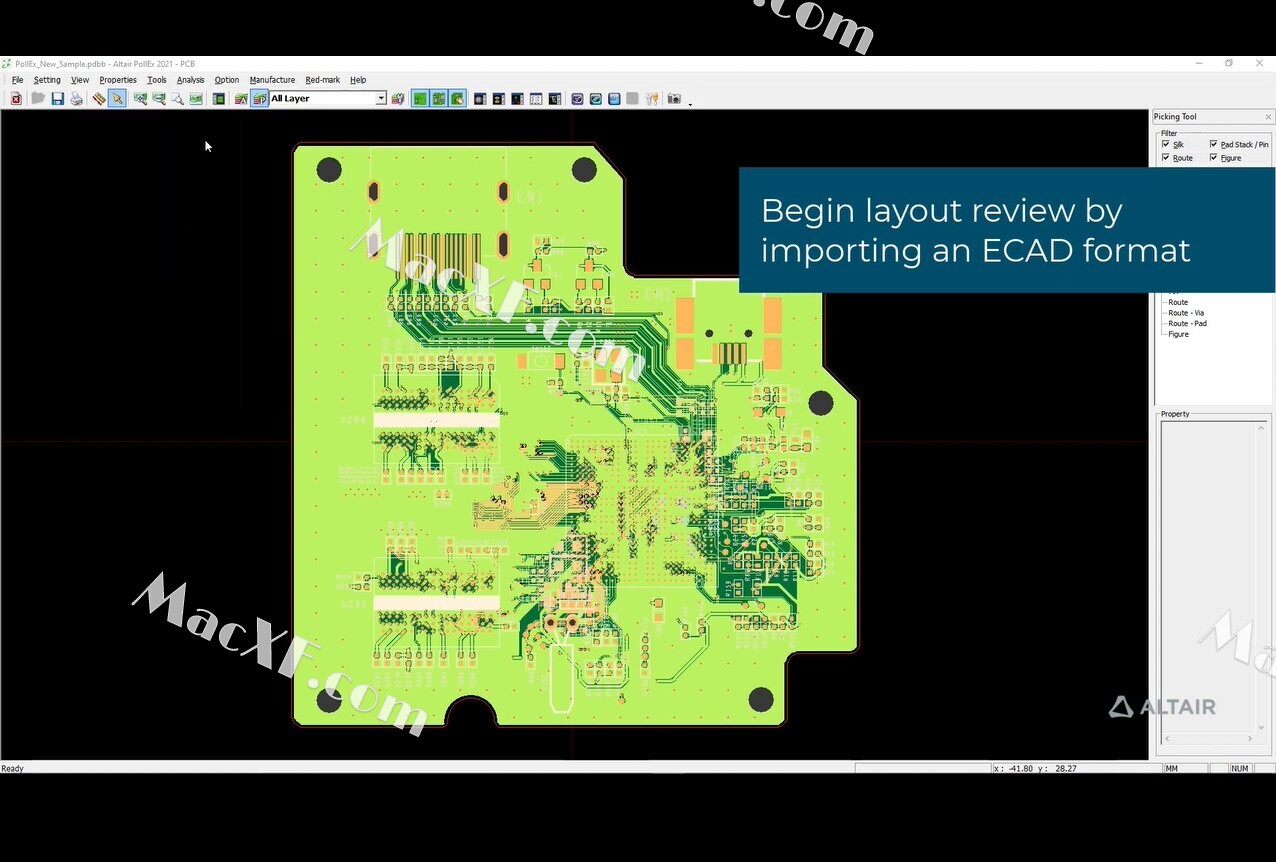

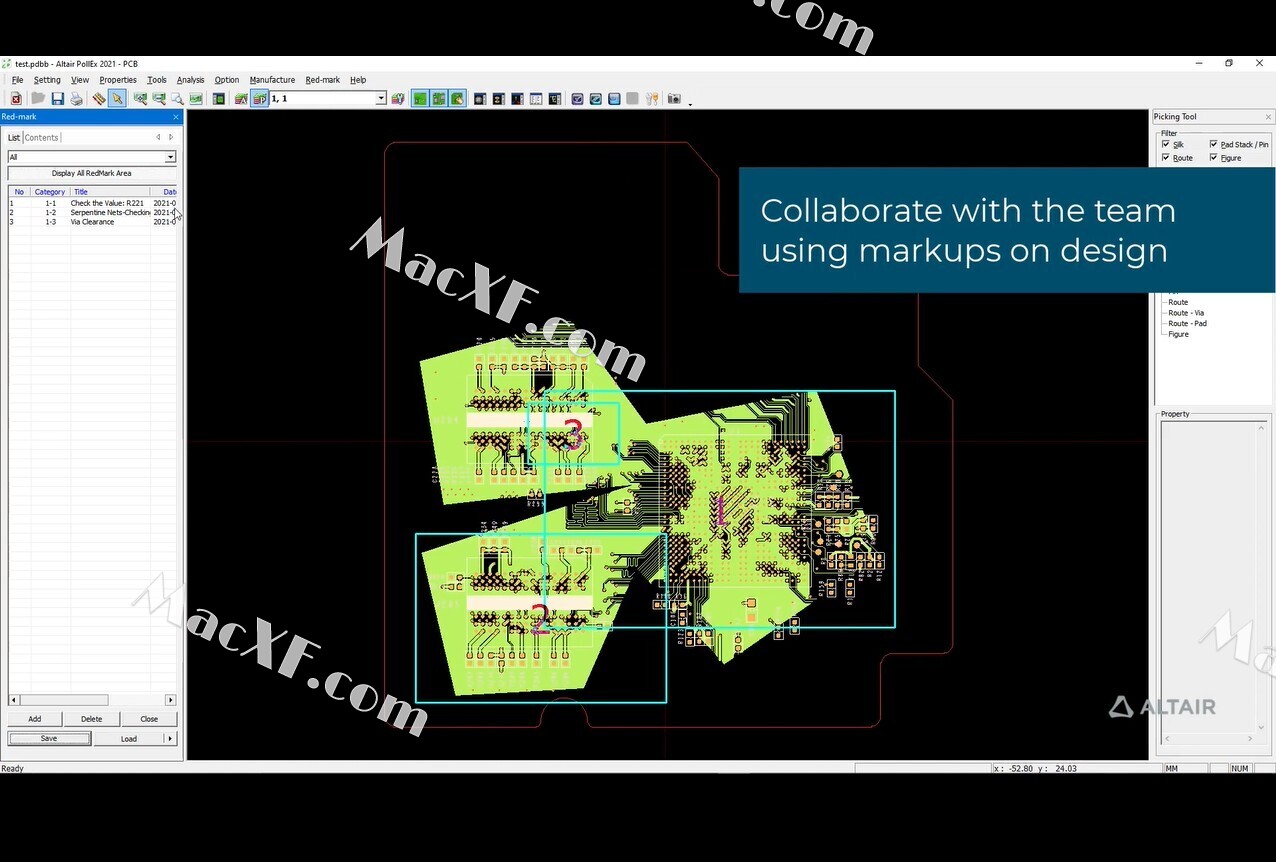

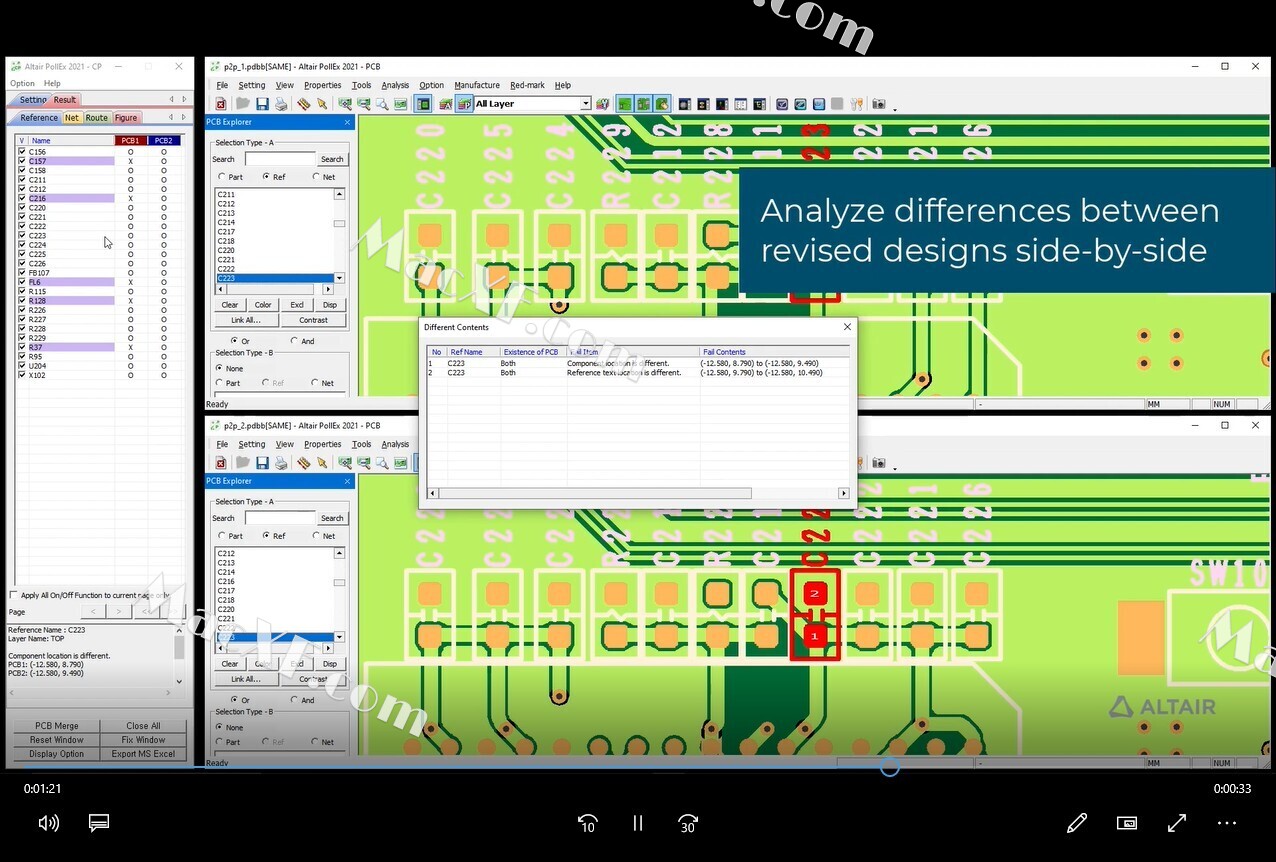

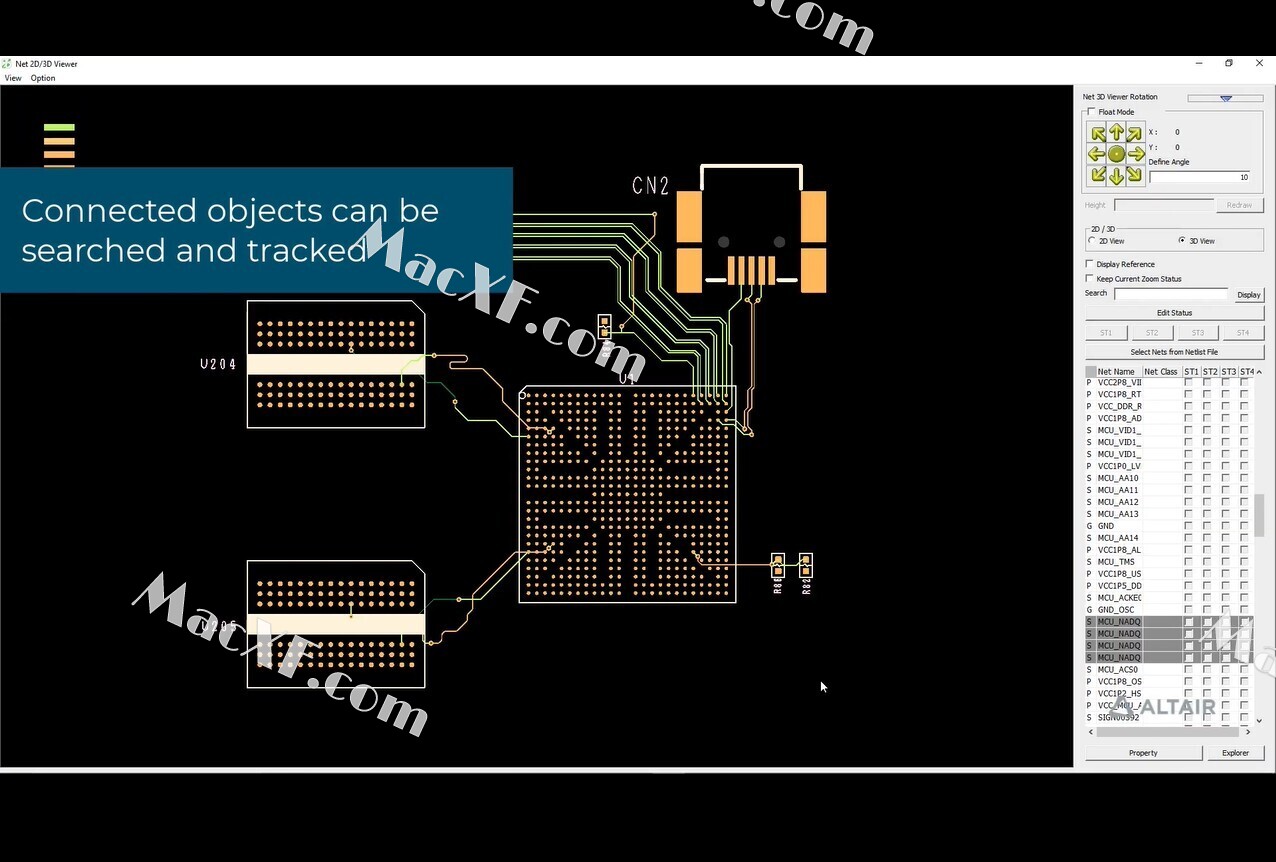

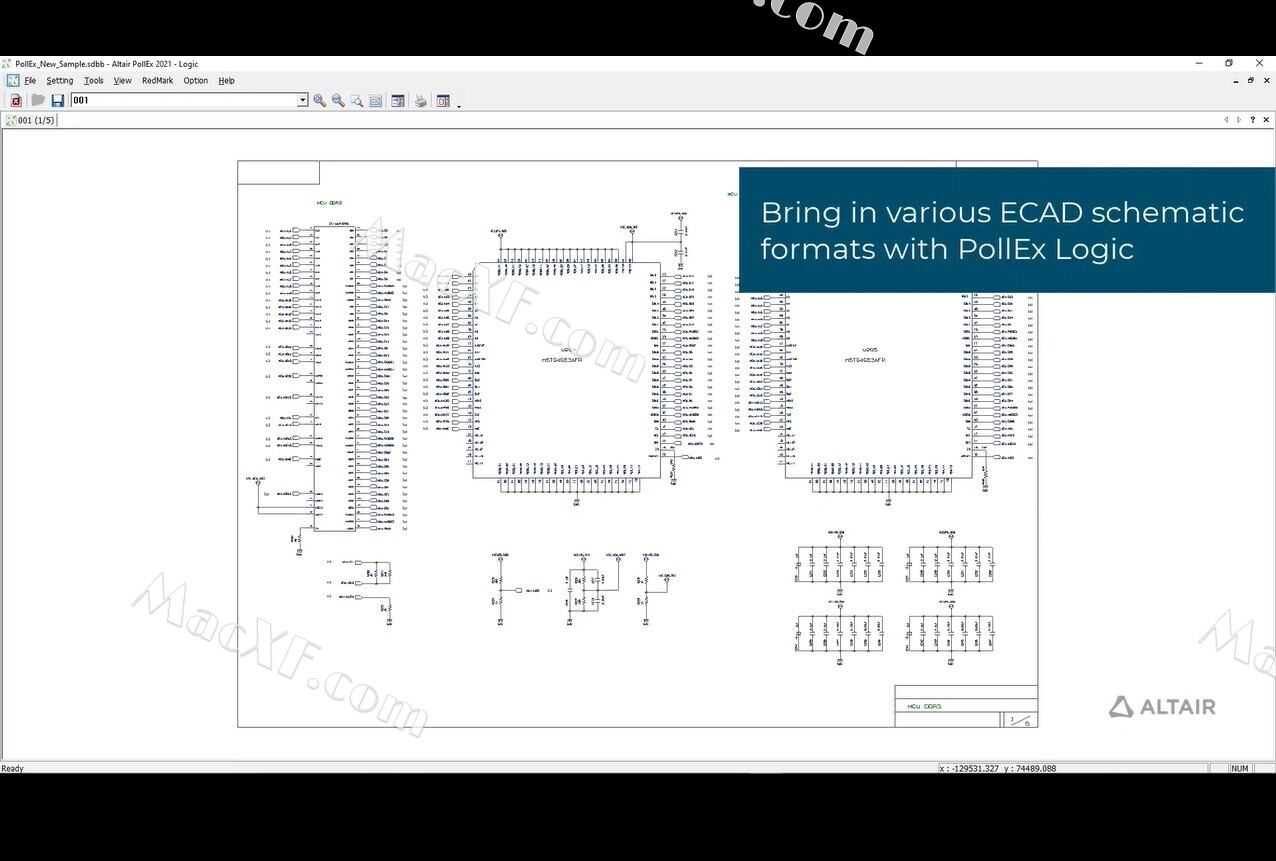

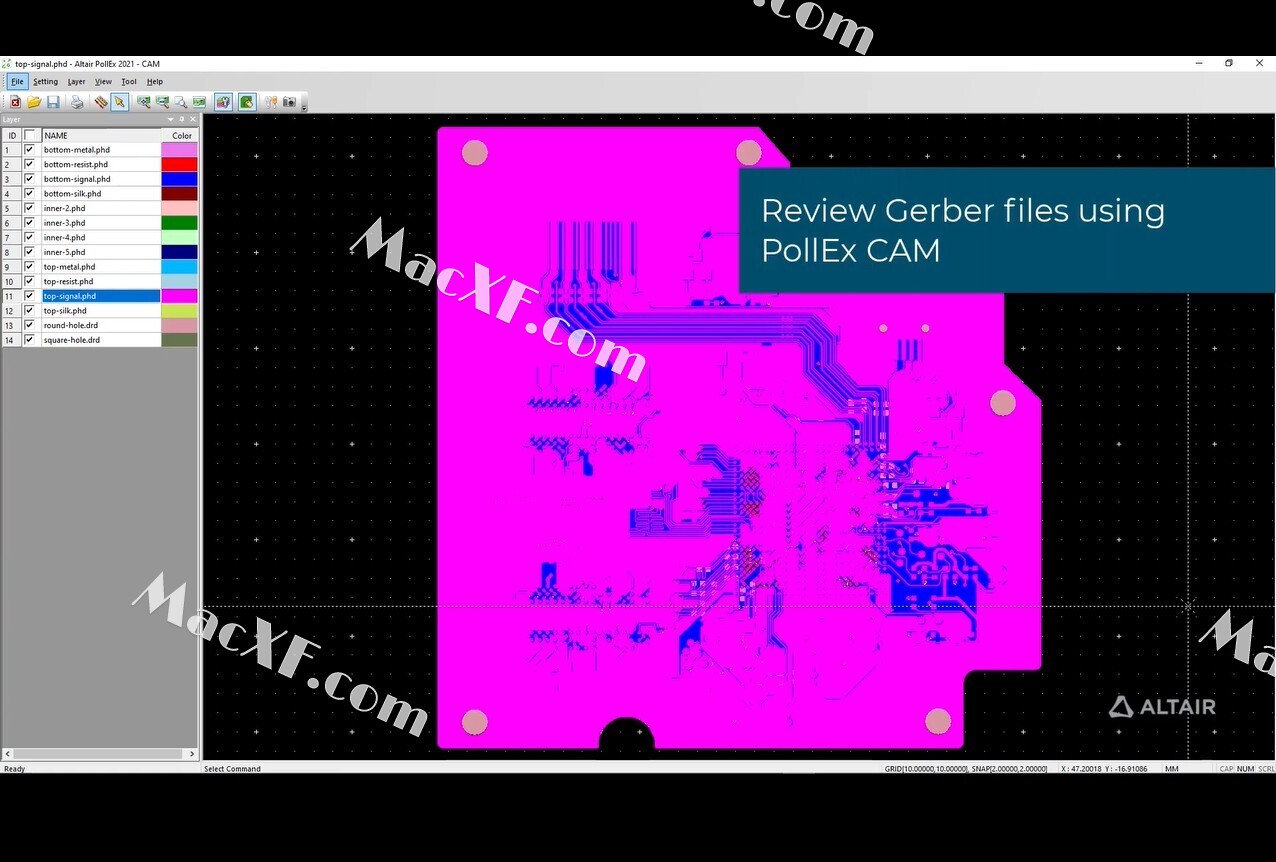

Altair PollEx 2021是一款功能强大的PCB设计软件,该软件不仅内置了强大PCB设计查看、分析和验证工具,还在强大的机械仿真软件基础上扩展到系统仿真和电磁学领域,这样便可以满足用户们的不同使用需求。另外软件还能针对所有相关 ECAD 系统、以及有着强大的PCB建模器,这两个强大的功能可以让用户们更好的探索设计细节。不过软件采用的是收费机制,对于个人用户而言价格太过昂贵。 今天小编就给大家带来了Altair PollEx 2021破解补丁,亲测可以完美激活软件,没有功能和使用时间上的限制,并且在下文附上了详细的图文软件安装破解教程,欢迎有需要的小伙伴们下载体验。

Altair PollEx 2021安装教程

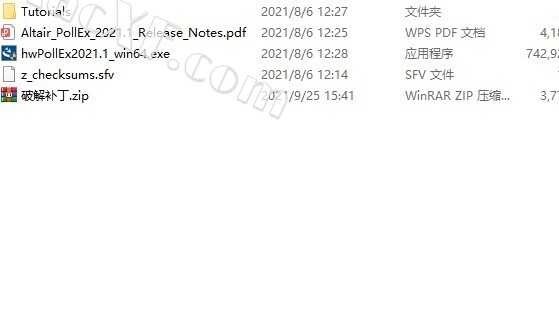

1下载解压,得到软件安装文件和破解补丁;

2运行hwPollEx2021_win64.exe开始安装,然后同意条款;

3选择软件安装路径,默认即可;

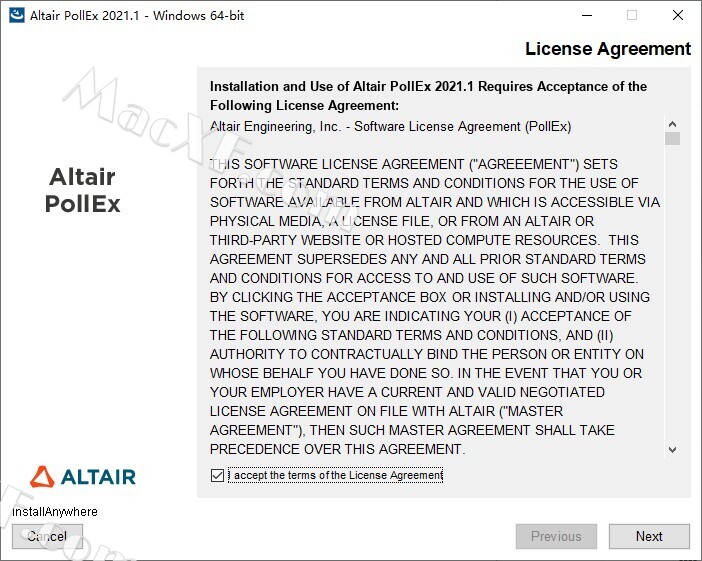

4选择创建快捷方式,方便之后运行;

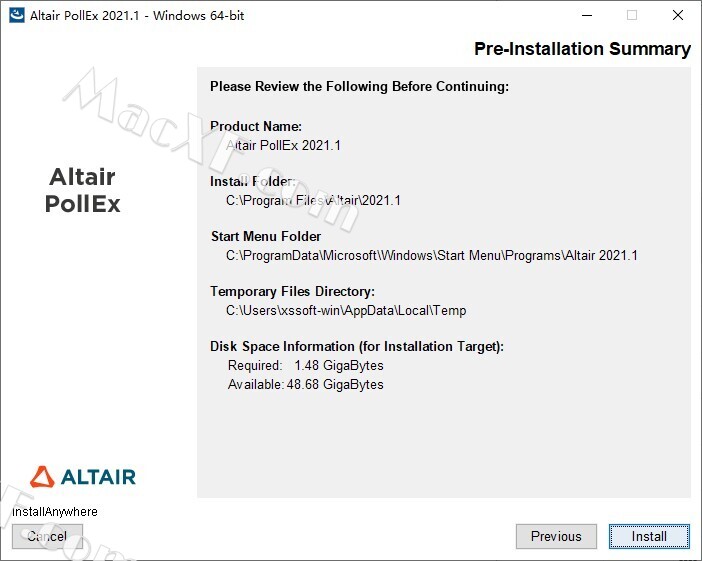

5点击安装

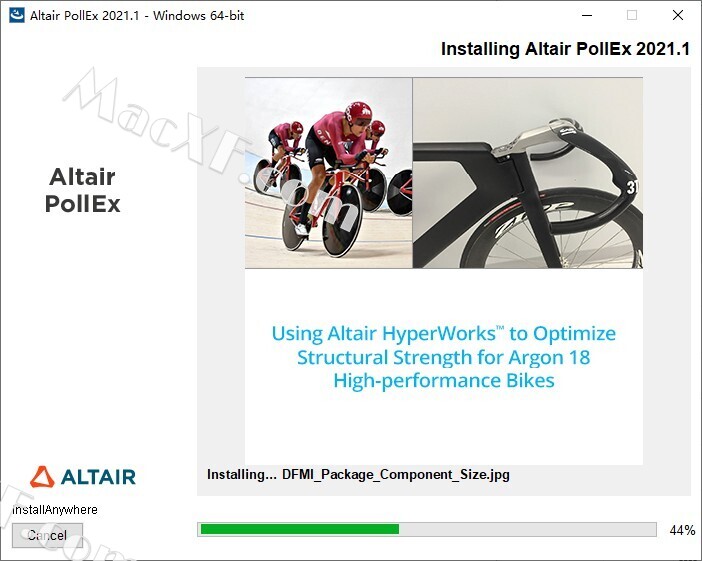

6正在安装

7安装完成,点击done退出引导;

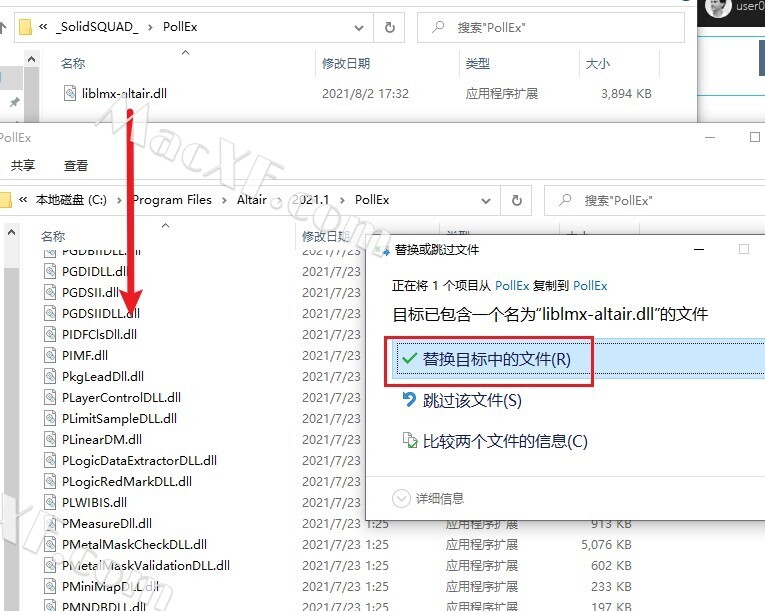

8将破解补丁复制到软件根目录下,如图所示; 默认路径:C:\Program Files\Altair\2021\PollEx

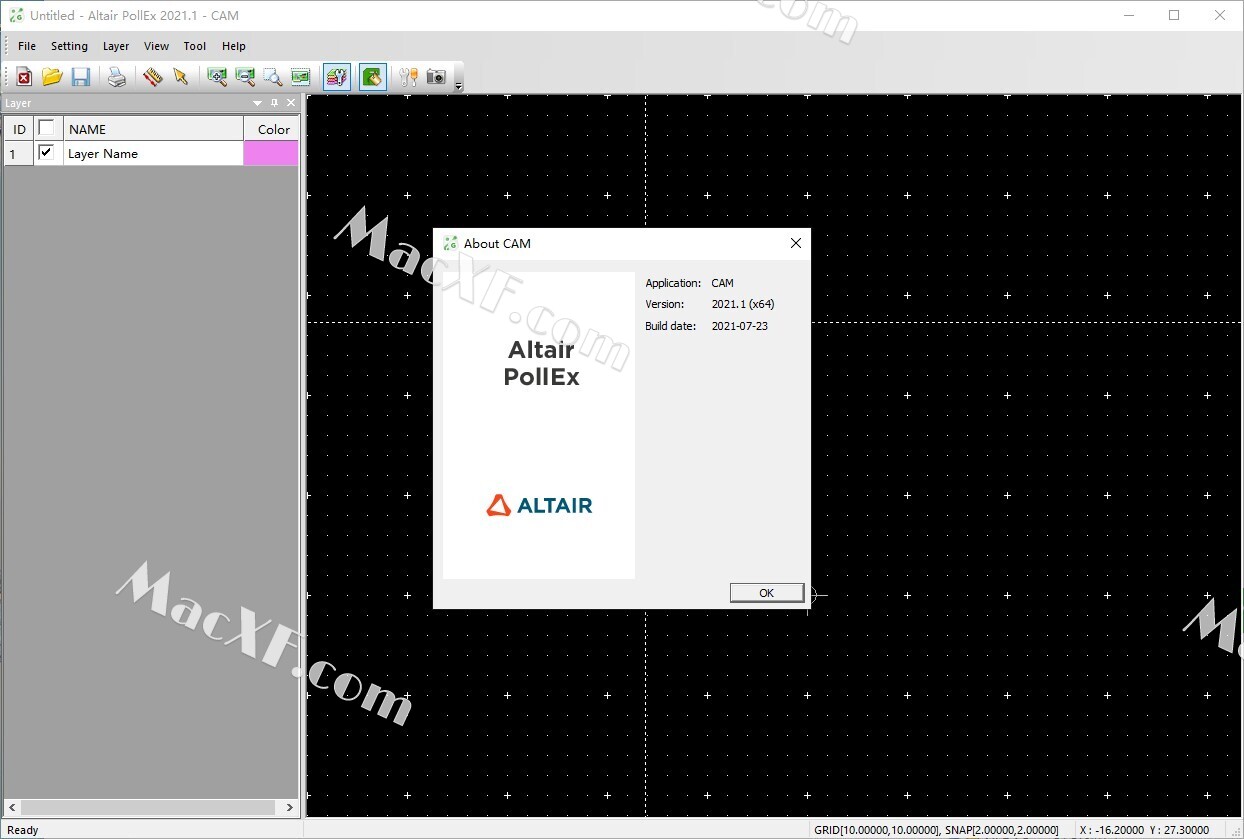

9软件安装完成,所有功能可免费使用

2021.1 版本的亮点

- 突出特点

-

添加和修改新的许可功能

-

新的许可功能代码:为 PollEx 制造选项添加了 PollExMFG,它将绘制相同的 30 个 AU。

-

更改了许可证功能代码:PollEx UPE 应用程序在 PollExBasic 功能中可用,它将从 30AU 中提取 10 个 AU。

- 添加 Altair 许可证实用程序

- 在 PollEx 2021.1 启动器中添加了 Altair 许可证实用程序。

- 添加 Altair License Management System 设置面板

- 安装过程中添加了环境变量设置面板。此面板仅在未设置环境变量时显示。

- 在 PollEx PCB 中添加设计数据保存选项

- 添加了将设计数据以压缩文件 (*.tgz) 保存在项目目录中以方便共享相关数据的功能。

- 添加了 SI Explorer

-

添加了支持预布局分析 SI Explorer 菜单的功能。添加了执行预布局分析的功能。PollEx SI Explorer 菜单允许在整个设计过程中验证设计决策,包括选择零件、添加材料、构建板层堆叠和创建网络拓扑。

-

执行 PollEx SI Explorer 后,会出现 SI Explorer 对话框。您可以从头开始进行布局前信号完整性分析。

-

创建层堆叠

-

创建 VIA 模型

-

创建传输线模型

-

创建网络拓扑(单端、差分、多耦合)

-

执行信号完整性分析(波形、眼图、网络参数)

- 添加功能以显示 S/Y/Z 参数

- 添加功能以在网络参数查看器 PollEx SI 中显示 S/Y/Z 参数。通过使用此功能,可以通过打开从各种条件中提取的 S/Y/Z 参数来进行比较和测量

- 添加自动化功能以支持多PCB 结构

- 添加了自动生成系统级网络拓扑的功能。通过使用此功能,可以在不同层叠的 PCB 之间进行多级拓扑配置和分析。

- 注意:在V2021.1 版本中,只能进行单网(Single-ended, Differential Pair)分析。V2021.2版本将发布多网络拓扑分析功能。

- 添加功能以支持刚性/柔性 PCB 设计

- 考虑到设计为刚性/柔性结构的设计的多重叠层结构,可以进行系统级信号完整性分析

- 添加特征提取SPICE Netlist

- 添加特征提取SPICE Netlist,可以选择和确定网络参数分析的结果。您可以指定网络分析的输出。(S/Y/Z 参数、Spice 网表、PSPICE 网表)

- S/Y/Z 参数:网络分析结果显示为 S/Y/Z 参数。

- Spice 网表:网络分析结果以 Berkeley Spice 兼容格式保存。(*.sp)

- PSPICE 网表:网络分析结果以 PSPICE 兼容格式保存。(*.lib)

- 添加了分配模拟输入的功能

- 添加了在网络分析期间应用模拟波形(例如正弦波)作为分析激励的功能

PollEx 2021.1 发行说明

PollEx 最显着的扩展和改进按组件列出

功能

- 添加了一项功能,可将设计数据保存在具有压缩文件 (*.tgz) 的项目目录中。

- 添加了使用网络串配对差分对网络的功能。

- 在Hole Through Pad 项中添加了Pad Measure Base 选项,用于设置焊盘和阻焊层的重叠区域(Pad+Solder Mask Overlap)。

- 在Copper Connected Pad 项中添加了一个Checking Type 选项,您可以选择连接铜宽比或裸铜面积比的类型。

- 在Net Group Shield 项目中添加了一个选项,如果在垂直屏蔽检查期间顶部或底部中的任何一个满足检查标准,则通过。

- 在Diff – Complete Shield 项目中添加了VIA Shielding 选项。

- 添加了使用UPE 中设置的部件分类自动设置组件/网络组的功能。

- 在输入对话框中添加了网络的输入设置菜单,以检查组件或网络的分组信息。

- 在IR Drop 中添加了一个选项以检查UPE 中注册的允许IR-Drop 值。

- 在PDB 阻抗中添加了一个选项以使用在UPE 中注册的目标阻抗值进行检查。

- 在结果表导出菜单中添加了一个选项以导出结果区域图像和 ECAD 链接信息。

- 在网络分析中添加了TDR 分析类型。使用此选项,可以分析从整个网络结构的驱动级看到的阻抗波形。在这个版本中,没有考虑多重反射,我们会在下一个版本中考虑。

- 在网络分析中添加了一个功能来选择和确定网络参数分析的结果。您可以使用此约束来指定网络分析的输出。

- S/Y/Z 参数:网络分析结果显示为 S/Y/Z 参数。

- Spice 网表:网络分析结果以 Berkeley Spice 兼容格式保存。(*.sp)。

- PSPICE 网表:网络分析结果以 PSPICE 兼容格式保存。(*.lib)。

- 添加了在网络分析中应用模拟波形的功能,例如正弦波作为分析激励。

- 添加了支持刚性/柔性PCB 设计的功能。通过使用此功能,考虑到设计为刚性/柔性结构的设计的多重叠层结构,系统级信号完整性分析成为可能。

- 添加了网络参数查看器以显示 S/Y/Z 参数。通过打开从各种条件中提取的 S/Y/Z 参数,可以进行比较和测量。

- 添加了在导入设计数据时指定钻孔层的选项。

- 添加了用于转换设计单位的命令行。

- 添加了用于创建UPF 文件(/EXPORT_UPFS) 的命令行。

- 添加了一个选项,用于在导入设计数据时为顶部和底部指定 Silk Layers。

已解决的问题

- 修改为在网络分析仪中分析眼图时在波形查看器中显示差分对网络的 Vdiff 波形。

- 修改以更改网络拓扑分析器中无源组件的值。

- 在网络分析中设置信号的运行速度时,增强了使用周期(ps) 和频率(MHz) 的能力。

- 增强了自动生成系统级网络拓扑的功能。启用了具有不同堆叠的 PCB 之间的多级拓扑配置和分析。

- 修改了 PDN 分析以在多边形直接连接到引脚时进行分析。

- 添加了一项功能,不仅可以分析有源组件的热量,还可以分析微量焦耳热量的影响。

- 添加了支持刚性/柔性PCB 的功能。通过使用此功能,可以考虑设计为刚性/柔性结构的设计的多重叠层结构进行热分析。

- 修复了使用功能符号添加逻辑符号时未应用分区名称的错误。

- 修复了生成包向导中SOD123 包尺寸不正确的错误。