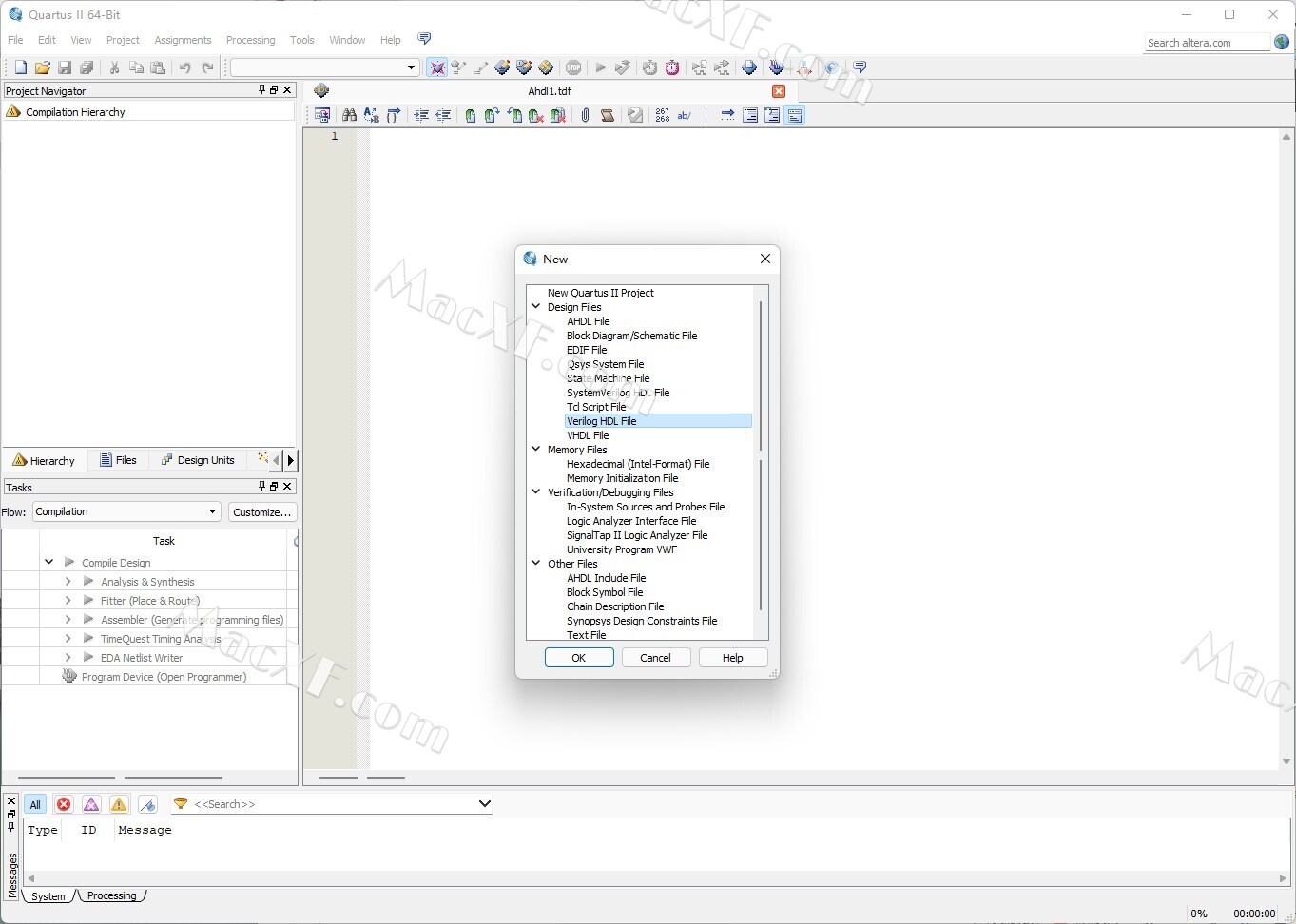

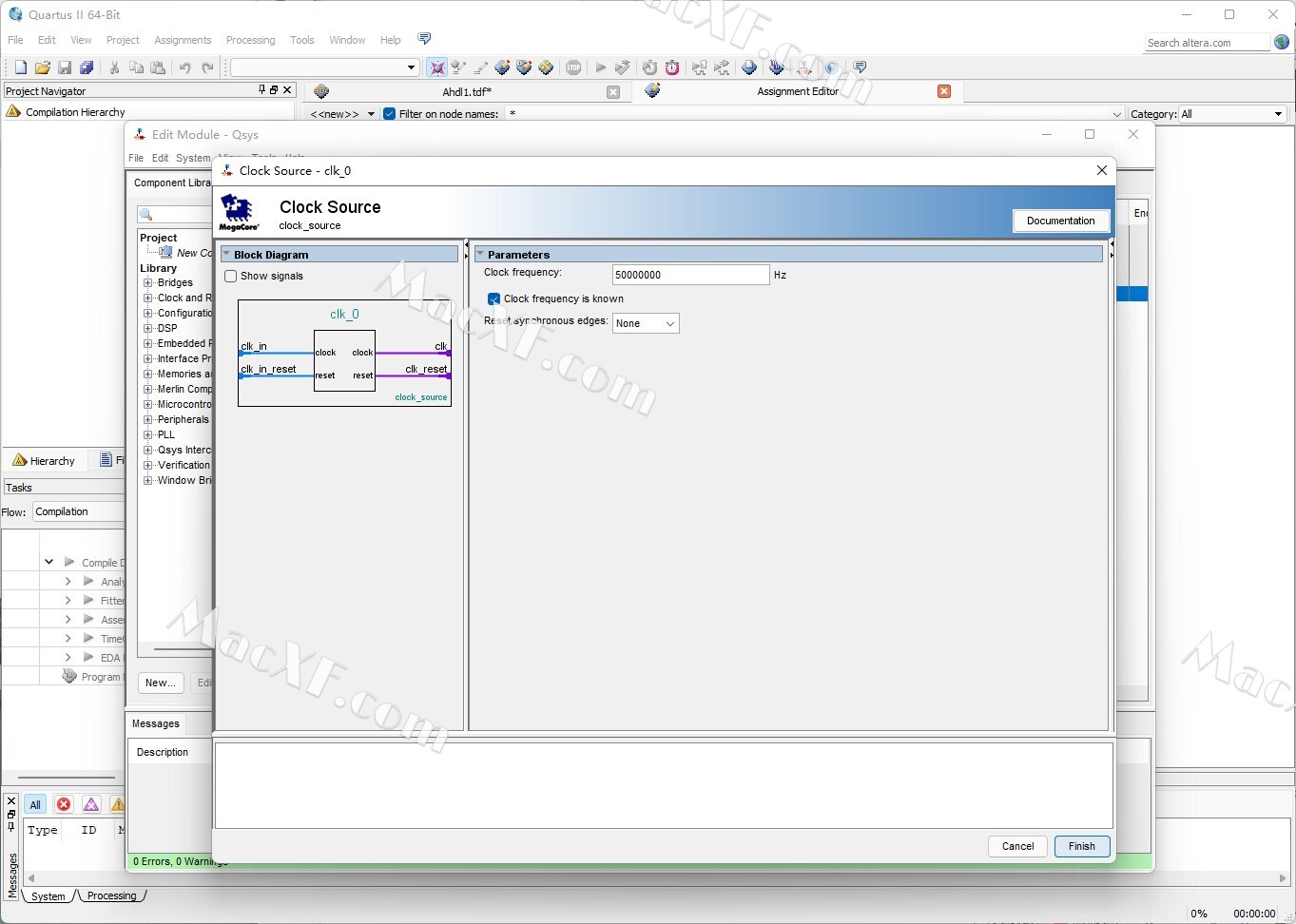

Quartus II 是Altera公司的综合性PLD/FPGA开发软件,支持原理图、VHDL、VerilogHDL以及AHDL等多种设计输入形式,Quartus II内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

破解教程

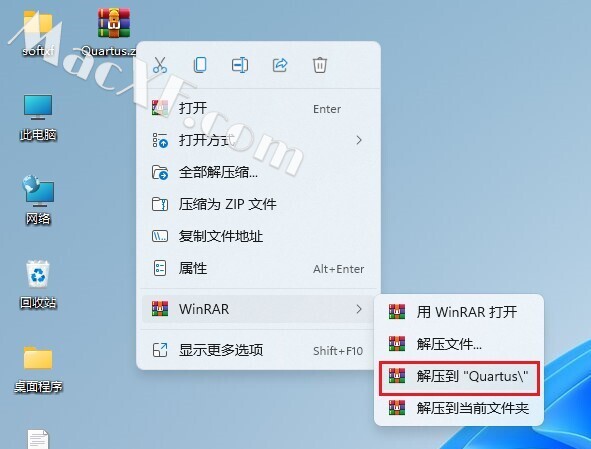

1下载完成后解压文件,鼠标右击【Quartus】压缩包选择【解压到 Quartus】。

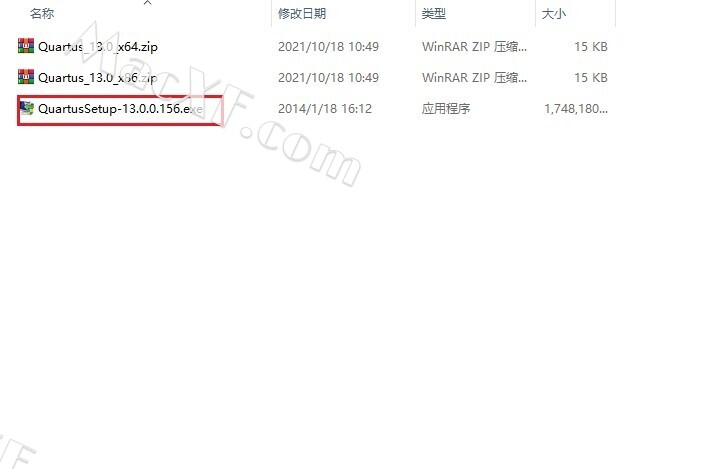

2打开解压后的文件夹,双击“QuartusSetup-13.0.0.156.exe”应用程序,开始安装。

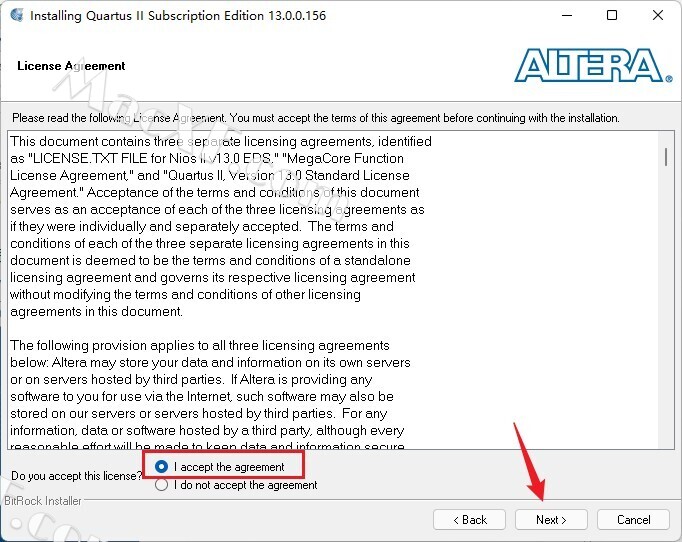

3点击“I accept the agreement”,点击“Next”

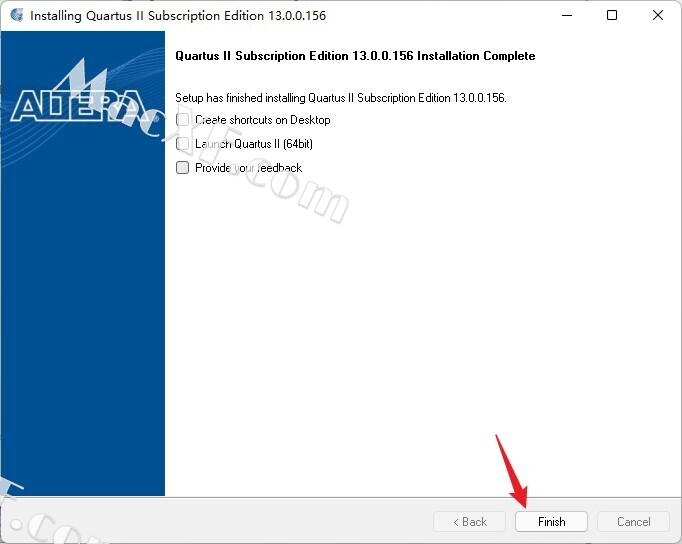

4一路默认安装即可,安装可能时间较长,请耐心等待,直到安装完成,点击“finish”。(安装默认路径为“C:\altera\13.0”)

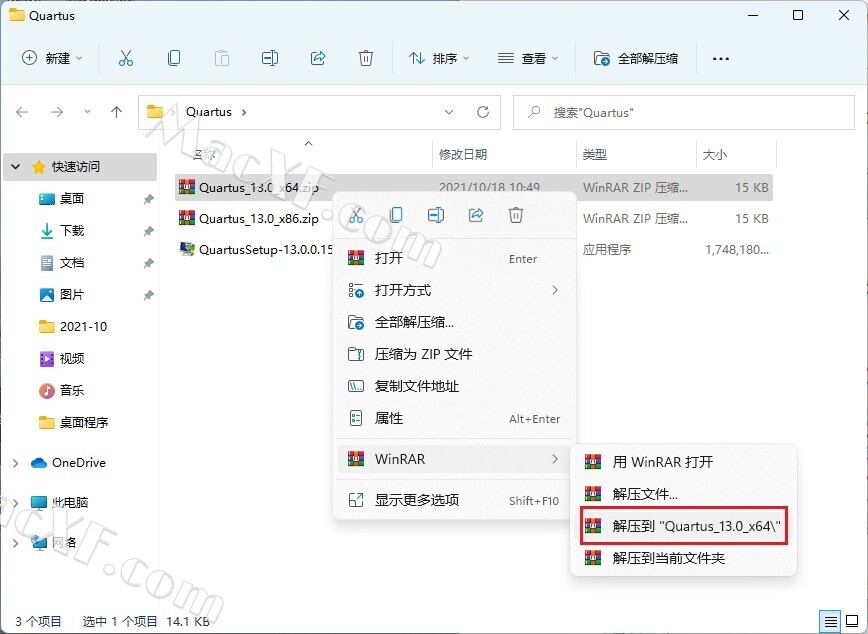

5安装完成后,在解压文件中找到适合自己电脑的破解器,解压并运行

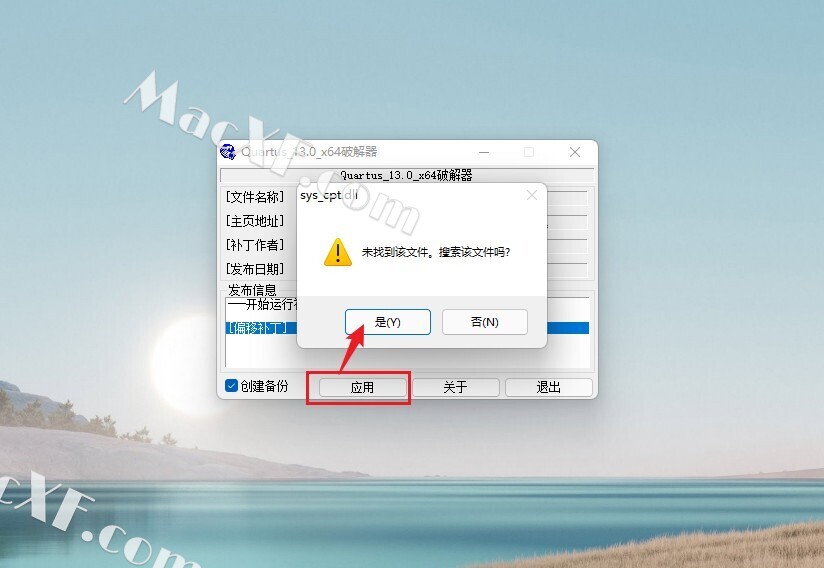

6按照如下步骤点击。

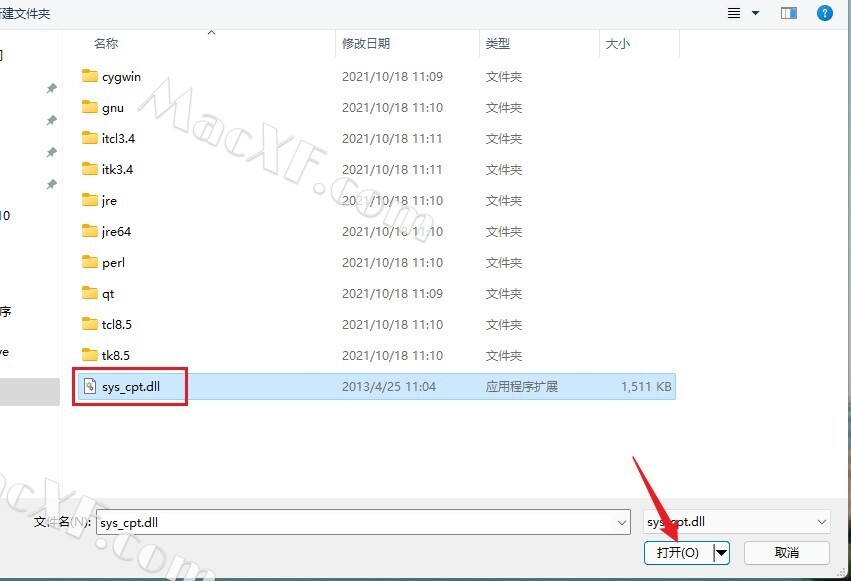

7选择“C:\altera\13.0\quartus\bin64\”里面的“sys_cpt.dll”文件。

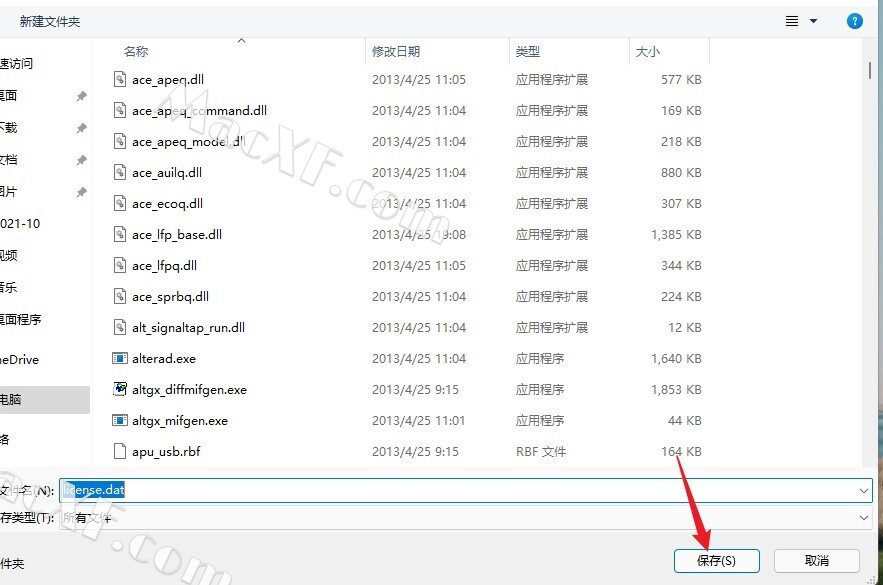

8此时会在安装目录下方生成一个“license”文件,点击“保存”就行了。

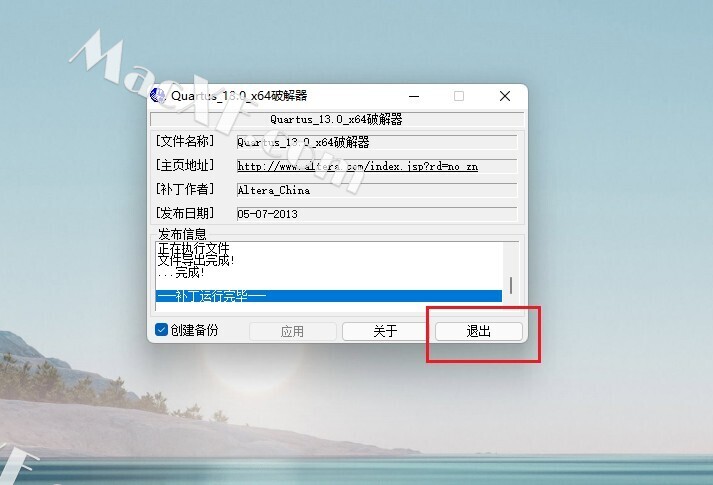

9最后,破解器会这样显示,点击“退出”。

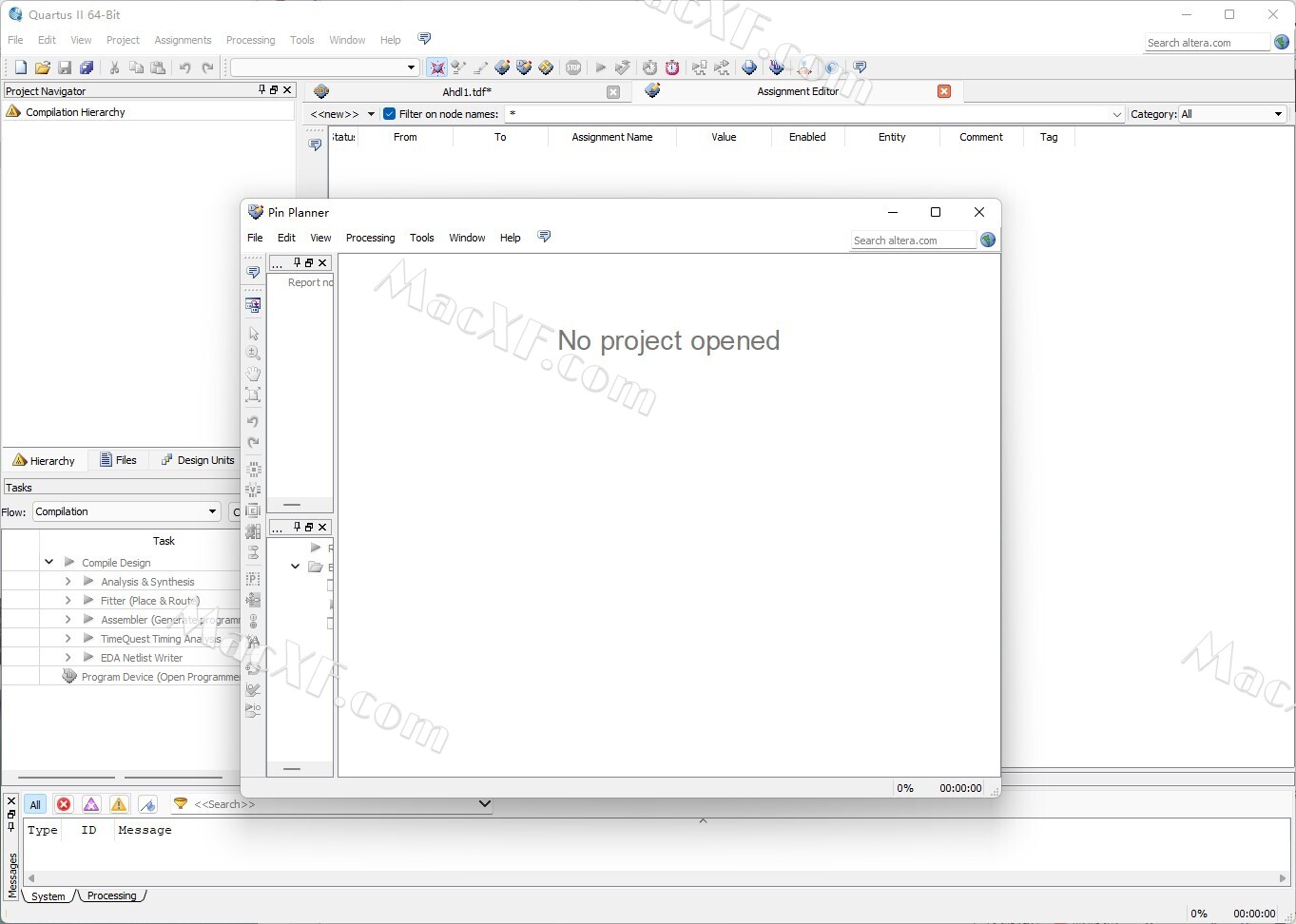

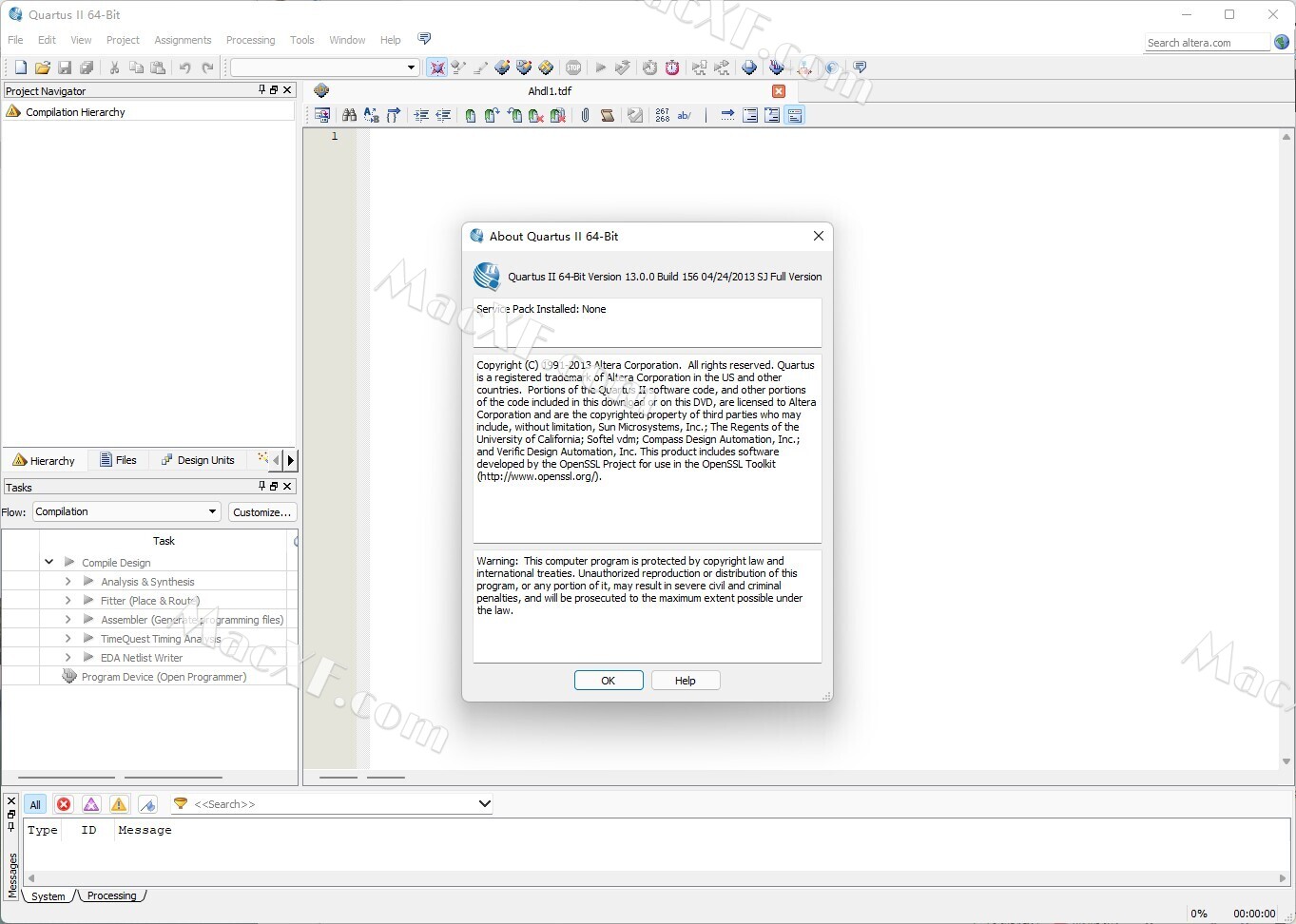

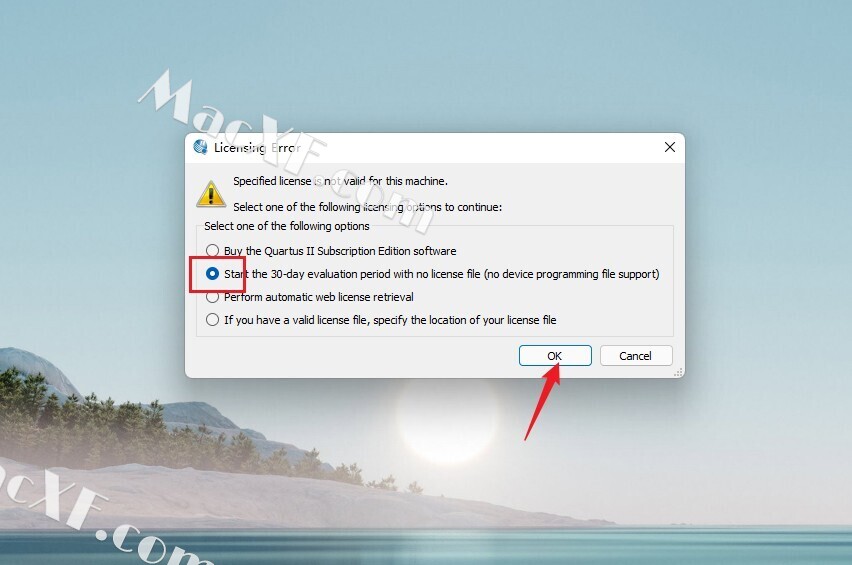

10运行桌面自动生成的“Quartus II 13.0(64-bit)”快捷方式,选择第二个,点击“ok”。

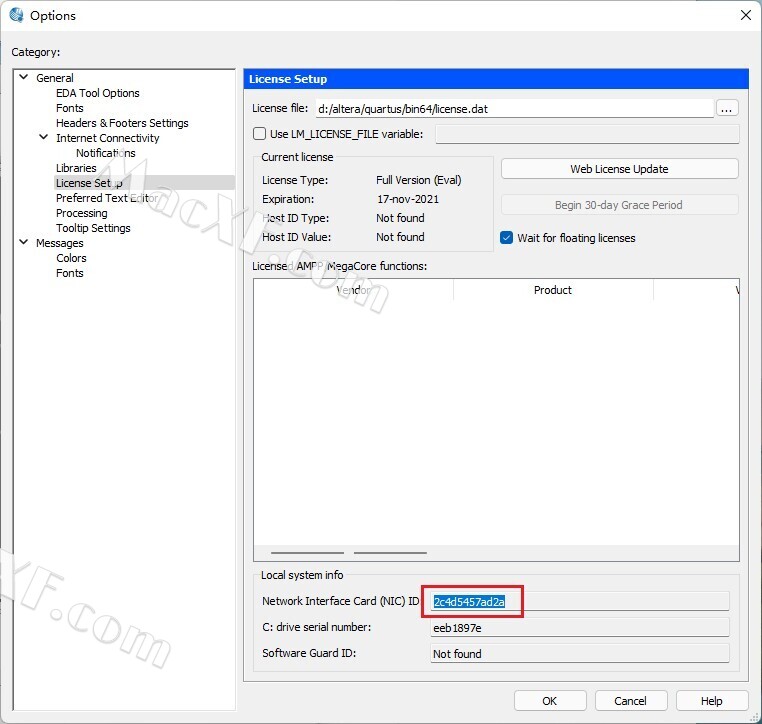

11选择“tools”下方的“license setup”后,会弹出如下窗口,将ID复制即可。

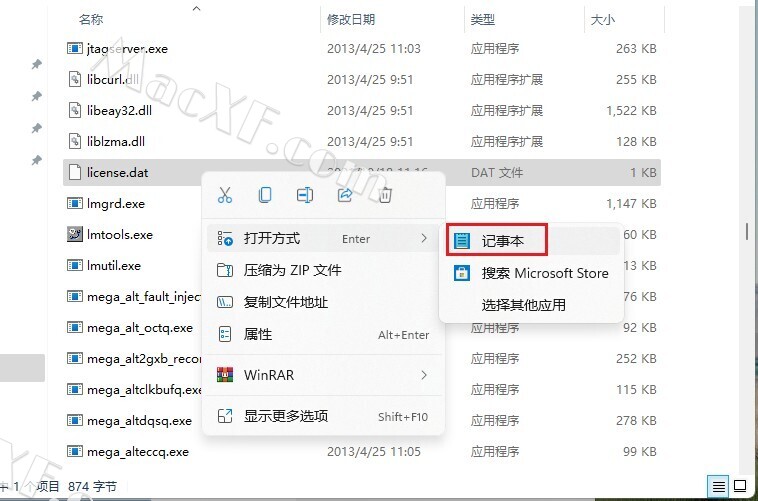

12在“C:\altera\13.0\quartus\bin64\”中找到“license”文件,并以记事本打开。

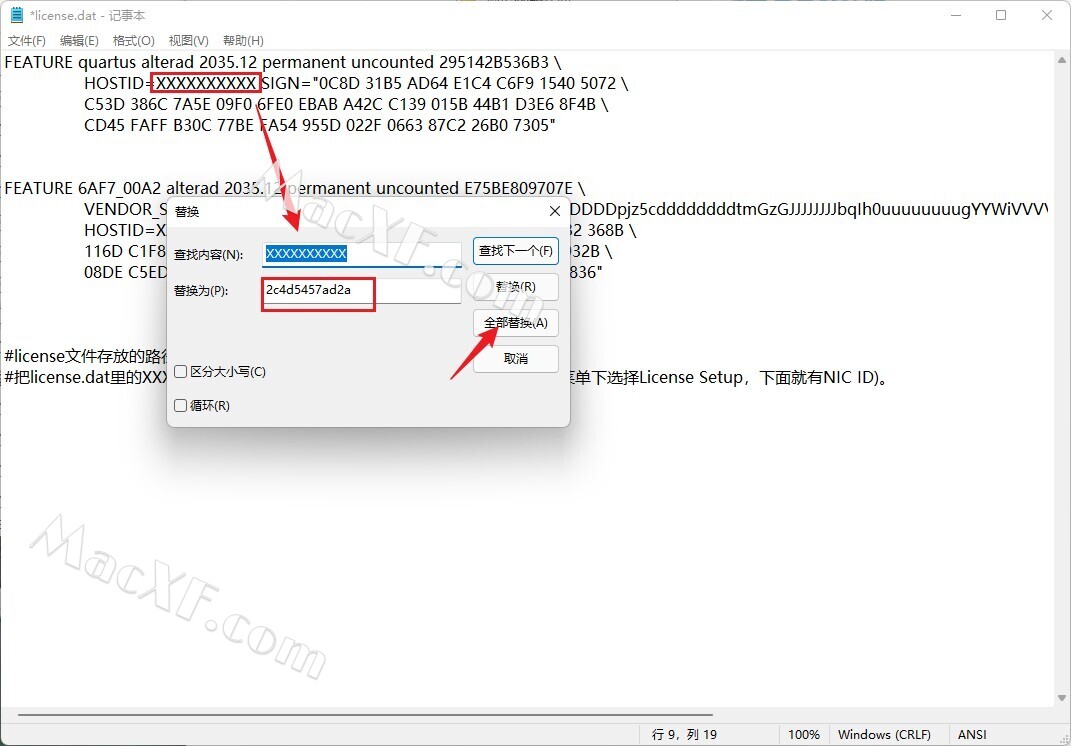

13将复制的ID替换所有的“XXXXXXXXXX”,保存后即可完成破解。

软件特色

- 支持MAX7000/MAX3000等乘积项器件

2.0版Quartus II设计软件现在除了支持Altera的APEX 20KE,APEX 20KC, APEX II,ARM的Excalibur嵌入处理器方案,Mercury,FLEX10KE和ACEX1K之外,还支持MAX3000A,MAX7000系列乘积项器件。MAX3000A和MAX7000设计者现在可 以使用QuartusII设计软件中才有的所有强大的功能。

- 软件体积缩小,运行速度加快

QuartusII2.0安装软件为290M,完全安装为700M,如果定制安装,不选择Excalibur嵌入处理器,则安装所需空间为 460M,比QuartusII1.1版本减少一半以上的空间要求,却能支持ALTERA全部芯片的开发。同时软件的装载,编译,仿真速度比1.1版本大 大加快。

- LogicLock设计流程把性能提升15%

- QuartusII2.0 设计软件通过增强层次LogicLock模块级设计方式,将性能平均改善15%。 LogicLock设计流程把整个模块的放置交由设计者控制,如果必要的话,可以采用辅助平面布置。LogicLock设计流程运行设计者单独地优化和锁定每个模块的性能,在大型SOPC设计的构建过程中也保持整个系统的性能。2.0版Quartus II设计软件把新的LogicLock设计流程算法集成到未来的Altera器 件中,该算法充分利用了模块级设计的优势。

- 采用快速适配选项缩短编译时间

QuartusII2.0增加了一个新的快速适配编译选项,选择中这个选项,将会比缺省设置要缩短50%的编译时间。快速适配功能保留了 最佳性能的设置,加快了编译过程。这样布局适配算法反复的次数更少,编译速度更快,对设计性能的影响最小。

- 新的功能减小了系统级验证

- 2.0版Quartus II设计软件引入了新的功能,加快验证过程,这通常是SOPC设计流程中最漫长的阶段。在最初的编译时间中,新的 SignalProbe技术允许用 户在保留设计最初布线,时限和设计文件的同时把内部节点引到未用的管脚进行分析。SignalProbe技术完成了现有SignalTap嵌入逻辑分析的功能。 而且,设计者能够使用新版本中提供的HDL测试模板快速地开发HDL仿真矢量。

- 2.0版 Quartus II设计软件也可以自动地从QuartusII仿真器波形文件中创建完整的HDL测试平台。

- 2.0版Quartus II设计软件也支持高速I/O设计,生成专用I/O缓冲信息规范(IBIS)模型导入到常用的EDA信号集成工具中。IBIS模型根据设计中每个管脚的I/O标准设置来定制,简化第三方工具的分析。

- 5.0版以上支持双核CPU的嵌入。

- Altera 公司每出一个新版本都会缩短其编译速度。因为它的编译速度实在是很慢。

- 内核,就是指软核(可以由使用者根据自己的需要定制相应的功能)可以用NIOS II实现。

主要功能

- Quartus II提供了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性,包括:

- 可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;

- 芯片(电路)平面布局连线编辑;

- LogicLock增量设计方法,用户可建立并优化系统,然后添加对原始系统的性能影响较小或无影响的后续模块;

- 功能强大的逻辑综合工具;

- 完备的电路功能仿真与时序逻辑仿真工具;

- 定时/时序分析与关键路径延时分析;

- 可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析;

- 支持软件源文件的添加和创建,并将它们链接起来生成编程文件;

- 使用组合编译方式可一次完成整体设计流程;

- 自动定位编译错误;

- 高效的期间编程与验证工具;

- 可读入标准的EDIF网表文件、VHDL网表文件和Verilog网表文件;

- 能生成第三方EDA软件使用的VHDL网表文件和Verilog网表文件。

相关软件

DecSoft App Builder(Web可视化开发工具)

2021.65 特别版

167.91 MB 2021-12-01

JetBrains RubyMine 2021(编程开发软件)

v2021.3 无限试用特别版

366 MB 2021-12-02

JetBrains PyCharm Pro 2021(Python编辑开发)

v2021.3中文永久激活版

532.47 MB 2021-12-02

JetBrains WebStorm 2021(Web前端开发工具)

v2021.3.0 无限激活版

351.47 MB 2021-11-30

JetBrains CLion 2021(专业C/C++集成开发环境)

v2021.3无限试用版

583.67 MB 2021-12-02

JetBrains GoLand 2021(Go语言开发环境)

v2021.3.1 无限试用激活版

398.69 MB 2021-12-25

Jetbrains Rider 2021(跨平台.NET IDE集成开发)

V2021.3.1无限试用激活版

722.36 MB 2021-12-11

Toad for Oracle 2021(数据库开发和管理工具)

v14.2.104.1069激活版

1.09 GB 2021-10-10

Android Studio(安卓开发环境)

v2023.3.1.20 特别版+便携版

1.12 GB 2024-06-12